Системная шина процессора. системная шина

Содержание:

Шины эвм их основные характеристики

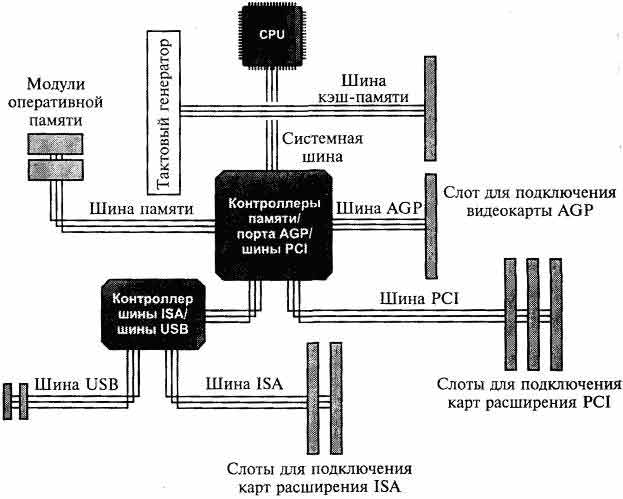

Шиной (Bus) называется вся совокупность линий (проводников на материнской плате), по которым обмениваются информацией компоненты и устройства ПК. Шина предназначена для обмена информацией между двумя и более устройствами. Шина, связывающая только два устройства, называется портом.

Шина имеет места для подключения внешних устройств — слоты, которые в результате становятся частью шины и могут обмениваться информацией со всеми другими подключенными к ней устройствами.

Локальная шина ввода/вывода — это скоростная шина, предназначенная для обмена информацией между быстродействующими периферийными устройствами (видеоадаптерами, сетевыми картами, картами сканера и др.) и системной шиной под управлением CPU. В настоящее время в качестве локальной шины используется шина PCI. Для ускорения ввода/вывода видеоданных и повышения производительности ПК при обработке трехмерных изображений корпорацией Intel была разработана шина AGP (Accelerated Graphics Port).

Стандартная шина ввода/вывода используется для подключения к перечисленным выше шинам более медленных устройств (например, мыши, клавиатуры, модемов, старых звуковых карт). До недавнего времени в качестве этой шины использовалась шина стандарта ISA. В настоящее время — шина USB.

Контроллер шины осуществляет управление процессом обмена данными и служебными сигналами и обычно выполняется в виде отдельной микросхемы либо в виде совместимого набора микросхем — Chipset.

Шина данных обеспечивает обмен данными между CPU, картами расширения, установленными в слоты, и памятью RAM. Чем выше разрядность шины, тем больше данных может быть передано за один такт и тем выше производительность ПК. Компьютеры с процессором 80286 имеют 16-разрядную шину данных, CPU 80386 и 80486 — 32-разрядную, а компьютеры с CPU семейства Pentium — 64-разрядную шину данных.

Шина адреса служит для указания адреса к какому-либо устройству ПК, с которым CPU производит обмен данными. Каждый компонент ПК, каждый регистр ввода/вывода и ячейка RAM имеют свой адрес и входят в общее адресное пространство PC. По шине адреса передается идентификационный код (адрес) отправителя и (или) получателя данных.

Шина управления передает ряд служебных сигналов: записи/считывания, готовности к приему/передаче данных, подтверждения приема данных, аппаратного прерывания, управления и других, чтобы обеспечить передачу данных.

Основные характеристики шины

Разрядность шины определяется числом параллельных проводников, входящих в нее. Первая шина ISA для IBM PC была восьмиразрядной, т. е. по ней можно было одновременно передавать 8 бит. Системные шины современных ПК, например, Pentium IV — 64-разрядные.

Пропускная способность шины определяется количеством байт информации, передаваемых по шине за секунду. Для определения пропускной способности шины необходимо умножить тактовую частоту шины на ее разрядность. Например, для 16-разрядной шины ISA пропускная способность определяется так:

(16 бит * 8,33 МГц): 8 = 16,66 Мбайт/с.

При расчете пропускной способности, например шины AGP, следует учитывать режим ее работы: благодаря увеличению в два раза тактовой частоты видеопроцессора и изменению протокола передачи данных удалось повысить пропускную способность шины в два (режим 2х) или в четыре (режим 4х) раза, что эквивалентно увеличению тактовой частоты шины в соответствующее число раз (до 133 и 266 МГц соответственно).

Внешние устройства к шинам подключаются посредством интерфейса (Interface — сопряжение), представляющего собой совокупность различных характеристик какого-либо периферийного устройства ПК, определяющих организацию обмена информацией между ним и центральным процессором.

К числу таких характеристик относятся электрические и временные параметры, набор управляющих сигналов, протокол обмена данными и конструктивные особенности подключения. Обмен данными между компонентами ПК возможен только если интерфейсы этих компонентов совместимы.

Системная шина

|

Общая структурная схем ЭВМ. |

Системные шины представляют собой набор соединительных проводников-линий, объединяющих одноименные выводы всех периферийных модулей. По каждой линии может быть передано значение одного разряда двоичного кода в виде уровней напряжения, соответствующих логическому нулю или логической единицы.

Системная шина служит для обеспечения связи между ЦП и различными периферийными устройствами и памятью машины. Шина содержит группы линий для передачи данных. Обычно этих линий в группе столько, сколько разрядов имеет машинное слово. Кроме того, име: ются адресные линии ( шина адресов), код на к торых определяет адреса ячеек памяти или внешних устройств, с которыми происходит обмен данными, и группа управляющих линий, с помощью которых задается управляющее действие ( например, передача данных в ЦП.

Системные шины представляют собой набор соединительных проводников — линий, объединяющих одноименные выводы всех периферийных модулей.

Системная шина включает: шину данных ( ШД), содержащую провода и схемы сопряжения для параллельной передачи всех разрядов числового кода ( машинного слова) операнда, шину адреса ( ША), состоящую из проводов и схем сопряжения для параллельной передачи всех разрядов кода адреса ячейки основной памяти или порта ввода-вывода внешнего устройства, шину управления ( ШУ), содержащую провода и схемы сопряжения для передачи инструкций ( управляющих сигналов, импульсов) во все блоки компьютера, и шину питания, имеющую провода и схемы сопряжения для подключения блоков ПК к системе энергопитания.

Системная шина служит для обеспечения связи между ЦП и различными периферийными устройствами и памятью машины. Шина содержит группы линий для передачи данных. Обычно этих линий в группе столько, сколько разрядов имеет машинное слово.

Системные шины представляют собой набор соединительных проводников — линий, объединяющих одноименные выводы всех периферийных модулей. По каждой линии может быть передано значение одного разряда двоичного кода в виде уровней напряжения. Обычно 0 3 и 2 4 В соответствуют лог. По роду передаваемой информации все линии разделены на три группы, образующие шину данных, шину адресов и шину управления. Так как рассматриваемый микропроцессор предназначен для обработки 8-разрядных двоичных чисел, то порты ввода или вывода тоже 8-разрядные.

Системная шина — основная интерфейсная система компьютера, обеспечивающая сопряжение и связь всех его устройств между собой.

Системная шина работает на частоте материнской платы, и это существенно снижает эффективное быстродействие компьютера. Наличие же backside — шины ускоряет обмен с кэш-памятью.

Системная шина ( магистраль) ISA была разработана специально для персональных компьютеров типа IBM PC AT и является фактическим стандартом. В то же время, отсутствие официального международного статуса магистрали ISA ( она не утверждена в качестве стандарта ни одним международным комитетом по стандартизации) приводит к тому, что многие производители допускают некоторые отклонения от фирменного стандарта.

|

Общая структурная схем ЭВМ. |

Системные шины представляют собой набор соединительных проводников-линий, объединяющих одноименные выводы всех периферийных модулей. По каждой линии может быть передано значение одного разряда двоичного кода в виде уровней напряжения, соответствующих логическому нулю или логической единицы.

Системные шины реализуются на основе многопроводных магистралей. Каждому устройству на шине присваивается адрес и уровень приоритета. Чем ближе расположено устройство к центральному процессору на системной шине, тем выше его приоритет при обработке прерываний. Обычно оперативная память располагается в непосредственной близости от центрального процессора, благодаря чему она имеет самый высокий приоритет.

Системная шина ( системный интерфейс) состоит из шин адреса и данных, 28 управляющих линий, 10 линий заземления и 4 линий электропитания. Шина адреса имеет 24 линии, 4 из которых зарезервированы.

Системная шина состоит из восьмислойной печатной платы и установленных на ней семи разъемов СМП34С — 135 на 135 контактов каждый. Платы в конструктиве устанавливаются произвольно.

Адресное пространствомикропроцессорного устройства.

Адресное пространство микропроцессорного

устройства изображается графически

прямоугольником, одна из сторон которого

представляет разрядность адресуемой ячейки

этого микропроцессора, а другая сторона — весь

диапазон доступных адресов для этого же

микропроцессора. Обычно в качестве

минимально адресуемой ячейки памяти

выбирается восьмиразрядная ячейка памяти (байт).

Диапазон доступных адресов

микропроцессора определяется разрядностью шины

адреса системной шины. При этом минимальный

номер ячейки памяти (адрес) будет равен 0, а

максимальный определяется из формулы:

Для шестнадцатиразрядной шины это будет число

65535 (64K). Адресное пространство этой шины и

распределение памяти микропроцессорной

системы, изображЈнной на рисунке 1, приведено на рисунке

2, а

распределение памяти микропроцессорной

системы, изображЈнной на рисунке 1, приведено на рисунке

3.

Рисунок 2. Адресное пространство шестнадцатиразрядной

шины адреса.

Рисунок 3. Распределение памяти микропроцессора с

шестнадцатиразрядной шиной адреса.

Микропроцессоры после включения питания и

выполнения процедуры сброса всегда начинают

выполнение программы с определЈнного адреса,

чаще всего нулевого. Однако есть и

исключения. Например процессоры, на основе

которых строятся универсальные компьютеры

IBM PC или Macintosh стартуют не с нулевого адреса. Программа должна храниться

в памяти, которая не стирается при выключении

питания, то есть в ПЗУ.

Выберем для

построения микропроцессорной системы микросхему ПЗУ

объЈмом 2 килобайта, как это показано на

рисунке 1. При рассмотрении построения

блока обработки сигналов мы договорились, что

процессор после сброса начинает работу с

нулевого адреса, поэтому разместим ПЗУ в

адресном пространстве начиная с нулевого адреса. Для того, чтобы нулевая ячейка

ПЗУ оказались расположенной по нулевому адресу адресного

пространства микропроцессора, старшие

разряды шины адреса должны быть равны 0.

При построении схемы необходимо

декодировать старшие пять разрядов адреса (определить,

чтобы они были равны 0). Это выполняется при помощи дешифратора

адреса, который в данном случае вырождается в

пятивходовую схему «ИЛИ-НЕ» Это связано с

тем, что внутри ПЗУ уже есть одиннадцативходовый

дешифратор адреса. При использовании

дешифратора адреса, обращение к ячейкам

памяти выше двух килобайт не приведЈт к

чтению ячеек ПЗУ, так как на входе выбора

кристалла CS уровень напряжения останется

высоким.

Теперь подключим микросхему ОЗУ. Для

примера выберем микросхему объЈмом 8 Кбайт.

Для выбора любой из ячеек этой микросхемы

достаточно тринадцатибитового адреса,

поэтому необходимо дополнительно

декодировать три оставшихся разряда адреса.

Так как начальные ячейки памяти адресного

пространства уже заняты ПЗУ, то использовать нельзя. Выберем

следующую комбинацию цифр 001 и используем

известные нам принципы .

Дешифратор адреса выродится в данном

случае в трЈхвходовую схему «И-НЕ» с

двумя инверторами на входе. Схема этого

дешифратора приведена на рисунке 1.

ПриведЈнный дешифратор адреса

обеспечивает нулевой уровень сигнала на

входе CS только при комбинации

старших бит 000

Обратите внимание, что так как объЈм ПЗУ

меньше объЈма ОЗУ, то между областью

адресов ПЗУ и областью адресов ОЗУ

образовалось пустое пространство

неиспользуемых адресов памяти

И, наконец, так как все

микропроцессоры предназначены для

обработки данных, поступающих извне, то в

любой микропроцессорной системе должны

присутствовать порты ввода-вывода.

Порт ввода-вывода отображается в адресное

пространство микропроцессорного

устройства как одиночная ячейка памяти,

поэтому порт ввода вывода можно разместить

по любому свободному адресу. Проще всего

построить дешифратор числа FFFFh. В этом

случае дешифратор превращается в обычную 16-ти

входовую схему «И-НЕ», поэтому и

выберем эту ячейку памяти в адресном

пространстве микропроцессора для

размещения порта ввода-вывода.

История

Первое поколение

Такие простые шины имели серьёзный недостаток для универсальных компьютеров. Всё оборудование на шине должно было передавать информацию на одной скорости и использовать один источник синхросигнала. Увеличение скорости процессора было не простым, так как требовало такого же ускорения всех устройств. Это часто приводило к ситуации, когда очень быстрым процессорам приходилось замедляться для возможности передачи информации некоторым устройствам. Хотя это допустимо для встраиваемых систем, данная проблема непозволительна для коммерческих компьютеров. Другая проблема состоит в том, что процессор требуется для любых операций, и когда он занят другими операциями, реальная пропускная способность шины может значительно страдать.

Такие компьютерные шины были сложны в настройке, при наличии широкого спектра оборудования. Например, каждая добавляемая карта расширения могла требовать установки множества переключателей для задания адреса памяти, адреса ввода-вывода, приоритетов и номеров прерываний.

Второе поколение

Компьютерные шины «второго поколения», например NuBus

решали некоторые из вышеперечисленных проблем. Они обычно разделяли компьютер на две «части», процессор и память в одной и различные устройства в другой. Между частями устанавливался специальный контроллер шин (bus controller

). Такая архитектура позволила ускорять скорость процессора без влияния на шину, разгрузить процессор от задач управления шиной. При помощи контроллера устройства на шине могли взаимодействовать друг с другом без вмешательства центрального процессора. Новые шины имели лучшую производительность, но также требовали более сложных карт расширения. Проблемы скорости часто решались увеличением разрядности шины данных , с 8-ми битных шин первого поколения до 16 или 32-х битных шин во втором поколении. Также появилась программная настройка устройств для упрощения подключения новых устройств, ныне стандартизованная как Plug-n-play .

Однако новые шины, так же как и предыдущее поколение, требовали одинаковых скоростей от устройств на одной шине. Процессор и память теперь были изолированы на собственной шине и их скорость росла быстрее, чем скорость переферийной шины. В результате, шины были слишком медленны для новых систем и машины страдали от нехватки данных. Один из примеров данной проблемы: видеокарты быстро совершенствовались, и им не хватало пропускной способности даже новых шин (PCI). Компьютеры стали включать в себя (AGP) только для работы с видеоадаптерами. В году AGP снова стало недостаточно быстрым для мощных видеокарт и AGP стал замещаться новой шиной PCI Express

Увеличивающееся число внешних устройств стало применять собственные шины. Когда были изобретены приводы дисков, они присоединялись к машине при помощи карты, подключаемой к шине. Из-за этого компьютеры имели много слотов расширения. Но в 1980‑х и 1990‑х были изобретены новые шины IDE

решившие эту проблему и оставив большую часть разъёмов расширения в новых системах пустыми. В наше время типичная машина поддерживает около пяти различных шин.

Шины стали разделять на внутренние (local bus

) и внешние (external bus

). Первые разработаны для подключения внутренних устройств, таких как видеоадаптеры и звуковые платы, а вторые предназначались для подключения внешних устройств, например, сканеров . IDE является внешней шиной по своему предназначению, но почти всегда используется внутри компьютера.

Третье поколение

Шины «третьего поколения» в настоящее время [когда?

]

находятся в процессе выхода на рынок, включая

Современные интегральные схемы часто разрабатываются из заранее созданных частей, так называемых «intellectual property» или IP. Разработаны шины (например Wishbone) для более простой интеграции различных частей интегральных схем.

Внешняя шина — данные

Внешняя шина данных выходит за пределы МП. Эти шины обеспечивают пропуск кодовой комбинации ( слова) на число разрядов, на которое рассчитан данный МП. У наиболее распространенных однокристальных МП ширина шины данных или магистрали составляет восемь разрядов. Связь внутри МП и с внешними устройствами осуществляется также с помощью шины адреса и шины управления.

Микросхемы представляют собой 16-битовый микропроцессор с 8-битовой внешней шиной данных ( центральное процессорное устройство с байтовым принципом организации) и предназначены для перевода аппаратных средств, построенных на К580ВМ80 и К580ВМ85, на программную среду К1810ВМ86 для повышения производительности. Различия состоят в изменении разрядности шины данных и соответствующих изменениях структуры и работы шинного интерфейса. БНЕзаме-нена линией состояния SSO, так как К1810ВМ88 может обращаться только к байтам и надобность в сигнале разрешения старшего байта шины SHE отпадает.

Как и процессор 8086, 80286 имеет 16-разрядную внешнюю шину данных и 6-байтный конвейер команд. Однако быстродействие процессора 80286 при тактовой частоте 12 5 МГц примерно в 6 раз выше, чем у 8086 с тактовой частотой 5 М Гц. Это достигается за счет усовершенствованной архитектуры и снижения количества тактов на одну команду.

Интегральная схема KJ810BM88 представляет собой 16-битовый микропроцессор с 8-битовой внешней шиной данных. Он предназначен прежде всего для перевода аппаратных средств, построенных на базе МП К580ВМ80 и К580ВМ85, на программную среду МП К1810ВМ86 с целью повышения производительности этих средств. Микропроцессоры ВМ86 и ВМ88 имеют аналогичную архитектуру и одинаковую систему команд. В ВМ88 сохранены 16-битовые общие и сегментные регистры, АЛУ для обработки 16-битовых операндов, сумматор для вычисления 20-битового физического адреса и средства поддержки многопроцессорных систем. Различия между этими двумя МП состоят в изменении разрядности шины данных и соответствующих изменениях структуры и работы шинного интерфейса.

|

Принцип двунаправленной, rj днных и алпеоа поелостав-передачи между внутренней и внеш — шин Данных и адреса., предосгав ней шинами данных ляя их в распоряжение внешних. |

Буферы данных и буферы адреса обеспечивают связь центрального процессора с внешними шинами данных и адреса. Особенность буферов состоит в том, что в каждом разряде они используют логические элементы с тремя состо-яниями.

Промежуточное положение между 8-разрядными и обычными 16-разрядными занимают 16-разрядные МП с 8-разрядной внешней шиной данных. Они представляют собой специальные модификации обычных 16-разрядных МП и обладают практически той же вычислительной мощностью, но в них используются более дешевые аппаратные схемы управления шиной.

Обмен 8-разрядными командами и данными между микропроцессором и внешними устройствами производится по 8-разрядной внешней шине данных DO — D7 через буферный регистр данных, который может находиться в трех состояниях — О, 1 и с высоким выходным сопротивлением, т.е. когда он отключается от внешней шины данных.

|

Структурная схема однокристального МП. |

Буферный регистр данных используется для временного хранения выбранного из памяти слова перед выдачей его во внешнюю шину данных. Его разрядность определяется количеством байтов информационного слова.

|

Типовая структура цифровой системы обработки сигналов. |

Как показано в табл. 2.5, в 1986 г. были выпущено много новых ПЦОС-СБИС; некоторые из них снабжены 32-разрядными внешними шинами данных, а в некоторых предусмотрена возможность арифметической обработки с плавающей запятой. Хорошим показателем производительности ПЦОС-СБИС является время выполнения 1024-точечного комплексного быстрого преобразования Фурье ( БПФ), так как этот вид обработки весьма характерен для многих применений.

Обмен 8-разрядными командами и данными между микропроцессором и внешними устройствами производится по 8-разрядной внешней шине данных DO — D7 через буферный регистр данных, который может находиться в трех состояниях — О, 1 и с высоким выходным сопротивлением, т.е. когда он отключается от внешней шины данных.

Снаружи процессор представляет собой 32-битовое устройство. Внешняя шина данных к памяти является 64-битовой, удваивая количество данных, передаваемых в течение одного шинного цикла.

Обмен кодами между памятью команд, памятью данных, периферийными устройствами и МП осуществляется через двунаправленный буфер шины данных. Последний изолирует внешнюю шину данных от внутренней. Это позволяет упростить подключение к одной шине нескольких устройств.

6. Шина PCI.

находятся

как бы в общем адресном

пространстве. Общее пространство

эмулируется с помощью таблицы

отображения адресов GART (Graphic Address Remapping

Table) блоками по 4 Кб. Таким образом копировать

данные из основной памяти в видеопамять

уже не требуется, этот процесс называют

AGP-текстурированием.

10. Шина PCI

Express.

Слоты PCI Express x4, x16, x1, опять x16,

внизу — стандартный 32-разрядный слот PCI

на материнской плате. использующая программную

модель шины PCI и высокопроизводительный физический

протокол, основанный на последовательной

передаче данных. Шина PCI Express нацелена на использование

только в качестве локальной шины.

Высокая производительность шины PCI Express

позволяет использовать её вместо шин AGP и тем более PCI и PCI Express заменила эти шины в ПК

Масштабируемость и универсальность — вот две основные

концепции, заложенные в архитектуре новой

шины PCI Express.

Универсальность шины PCI Express должна заключаться в том,

чтобы она заменила шину, связывающую

северный мост чипсета с графическим адаптером,

шину, объединяющую северный и южный мосты

чипсета, а также PCI-шину.

Масштабируемость шины PCI Express состоит в том, что шина позволяет

наращивать пропускную способность от

2,5 Гбит/с вплоть до 10 Гбайт/с (80 Гбит/с).

Для подключения устройства PCI Express используется двунаправленное последовательное

соединение точка-точка (lane), это отличается от

PCI, в которой все устройства подключаются

к общей 32-разрядной параллельной однонаправленной

шине.

11. Шина АТА

и Serial ATA.

ATA (Advanced Technology Attachment) — интерфейс подключения накопителей (например, жёстких дисков или оптических приводов) Он ограничивает емкость одного накопителя

504 Мбайт. ATA стали именовать Parallel ATA, имея

в виду, способ передачи данных по 40-жильному

кабелю.

Serial ATA позволяет передавать

информацию со скоростью 1.2 Gbps,

то есть 150 MBps. Один канал —

одно устройство, никаких перемычек, у шлейфа два оконечных разъема

— один для контроллера, второй для винчестера

(CD, DVD, etc). В современных компьютерах все

чаще стала использоваться SАТА шина, результатом

этого стало не только увеличение пропускной

способности, но и изменение внешнего

вида. Внешний вид шины стал более эргономичен

и удобен в использовании.

12. Шина USB.

| USB Тип А |

USB Тип B mini |

USB Тип В |

USB (Universal Serial Bus) — универсальная

последовательная шина, предназначенная

для периферийных устройств.

Шина USB представляет собой последовательный интерфейс передачи данных для среднескоростных

и низкоскоростных периферийных устройств.

USB-кабель представляет собой две витые

пары: по одной паре происходит

передача данных в каждом направлении

(дифференциальное вкл и т.д……………..